所属领域: A 电子信息技术

技术成果简介

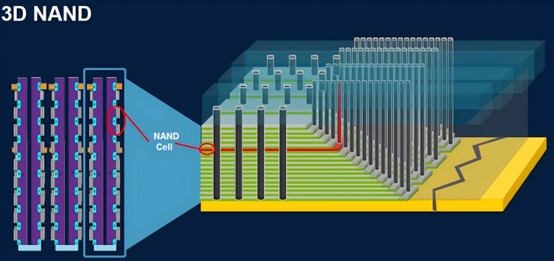

- 建立通用的高精度3D闪存器件可靠性模型基于多种3D闪存芯片的测试数据集,采用机器学习方法,将3D闪存器件中存在的多维噪音干扰和多层结构差异因素作为输入,建立通用的高精度3D闪存器件可靠性模型。首先,采取适用于拟合光滑曲线的浅层神经网络,建立闪存单元阈值电压分布模型。该模型能够提供更精准的纠错码译码信息和读参考电压,从而提高数据读取速度和降低比特错误率。然后,考虑到3D闪存堆叠层次间原始误码率分布呈现非平滑的锯齿状分布,采用基于梯度提升决策树的集成学习方法建立闪存单元原始比特错误率分布模型。该模型有助于发掘和预测闪存单元原始比特错误率变化趋势和分布特征,从而为设计可靠性优化技术提供依据。通过分析影响3D闪存阈值电压分布的相关因素,包括数据保存时间、堆叠层、可编程擦写次数(Program/Erase, P/E)、读干扰和状态内差异,如图1所示。利用神经网络模型对3D闪存阈值电压分布模型进行预测,将P/E次数记为pe、数据保存时间记为dr,读次数记为rd和字线记为wl作为神经网络的输入,阈值电压分布的离散点作为输出,如图2所示。提出的建模方法相比传统的建模方法能够提升预测精度。2. 高性能LDPC纠错码对于3D闪存而言,随着数据保存时间和可编程擦写周期的增加,原始误码率较高,引起较多的译码迭代次数,引起高的译码延迟问题。为了降低译码迭代次数和译码延迟,提出比特错误感知的自适应码率的LDPC方案。首先基于FPGA硬件测试平台,研究三维电荷俘获型TLC闪存比特错误特征。然后利用这些特征研究强纠错能力的LDPC码纠错方案,根据比特错误率的变化自适应地选择合适的码率进行译码,同时根据比特错误的非对称性调整译码似然比信息的权重值,以提升LDPC译码纠错性能,如图5和图6所示。

技术成果前景

3D闪存已经成为消费及工业类电子产品中的主要存储器件,并在数据中心和企业服务器中得到越来越广泛的应用。数据存储需求持续快速增长,对3D闪存器件的密度和可靠性不断提出更高要求。通用的高精度3D闪存器件可靠性模型与高性能纠错码技术是应对以上挑战的关键,对于闪存芯片制造商、闪存控制器和设备厂商具有重要意义。

联系人信息

联系人: 苏经理

联系电话: 0311-89687911

E-mail: hbskjcgzjzx@163.com

通讯地址: 石家庄科技大厦一楼西展厅